Volume 7, No.6, November - December 2018

International Journal of Advanced Trends in Computer Science and Engineering Available Online at http://www.warse.org/IJATCSE/static/pdf/file/ijatcse21762018.pdf

https://doi.org/10.30534/ijatcse/2018/21762018

# Analysis and Reduction of high power consumption using parallel prefix adder

<sup>1</sup>P.Sowndarya Mala, <sup>2</sup>N.M.Ramalingeswara Rao, <sup>3</sup>V.Sreevani, <sup>4</sup>M.Sai

<sup>1,2,3,4</sup>, Department of ECE, Godavari Institute of Engineering & Technology, Rajahmundry, A.P, India.

# ABSTRACT

An unconventional non-weighted number system that has gained a great scientific interest is the RNS (residue number system) that is high speed arithmetic, proficient of parallel, and carry-free. It utilizes number residues, in specific modulus for its representation. The design of reverse converter is based on modular address and regular adders that lead increase in power consumption and low speed. This is the main reason which prevents the use of Residue Number system in many applications. The parallel prefix based adder components is utilized to resolve the consumption issue of high power and supply enhanced tradeoff among delay and power consumption.

**Keywords:** Parallel Prefix adder, Reverse converter, Residue number system

#### 1. INTRODUCTION

In day to day life Embedded systems have been transformed from single-function control frameworks to highly complex system. Embedded systems like the portable multimedia and communication gadgets, personal wireless communication have created stringent requirements such as price, performance, power. These battery-powered gadgets have created a demand for low-priced, power efficient and high performance embedded processors [1-3] The RNS (residue number system) plays a major role in such devices due to competitive delay and low power feature. The RNS was used in the execution of fast arithmetic and fault tolerance in digital systems. The RNS requires forward and reverse conversion. However in reverse conversion the conversion stages are very critical in the evaluation of presentation of overall RNS. [4] Compared to other step reverse conversion leads to more delay. Hence the reverse conversion process initiates more overhead in terms of complexity and speedis more difficult in computation of the process. To develop the presentation of the converters, well-known adder architectures were used. To execute CPAs (carry-propagate adders), such as ripple-carry architectures and CSAs (carrysave adders) is used. The ones with parallel-prefix architectures are the fastest and expensive adders. The parallel-prefix adder [5] usage is to execute converters highly rises the speed and reduces the consumption issue of the power.

#### 2. RELATED WORK

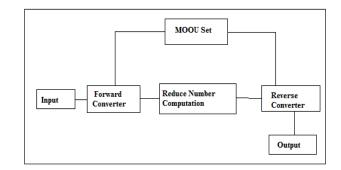

The residue number system encodes a huge number into a small numbers which consequences in substantial speed up of complete data processing. Each large integer might be portrayed as a set of smaller [3] integers named the residues. Three main steps involved in RNS are forward conversion, arithmetic computation and reverse conversion. The process of encoding input data into RNS representation is known as forward conversion. This procedure can be done by dividing the given conventional number by the entire module in the module set and finding the remainders of the divisions. The Reverse [5] Conversion is the procedure of converting RNS representation into conventional representation. Distinct module sets have to be chosen as shown in figure 1. The hardware modules assortment is a key to the performance of RNS. The use of parallel prefix adder based on different architecture with distinct structure such as Kogge–Stone (KS) and Brent—Kung adder shows a significant increase in performance [6].

# Figure 1: Block Diagram of RNS system 2.1 Parallel Prefix Adder

The quicker operation in reverse converter design was achieved with the help of parallel prefix structure.

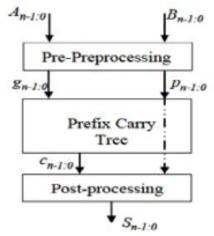

Figure 2: Block diagram of parallel prefix structure

As in figure 2 there are three main blocks in parallel prefix structure; they are prefix carry tree, pre-processing block, and post processing block. The procedure of the adder initiates with pre-processing phase [7] [11] by producing the Propagate (Pi) and Generate (Gi) shown in (eq 1), (eq 3). In prefix carry tree the prior block signal output all carry the bit signal. These stages comprise 3 logic complex cells. They are Buffer cell, Grey cell, and Black cell. The Grey cell performs only generate (G(i,j)). The black cell is used to calculate the propagate (P(i,j)), and the generate (G(i,j)) are shown in the (eq 3), (eq 4). The post processing block obtains the carry bits produced in the  $2^{nd}$  phase, which produces the sum and the equation is given [8]. The block diagram is shown in the Fig1

| Gm:n=An·Bn                              | (1) |

|-----------------------------------------|-----|

| G0=Cin                                  | (2) |

| Pm:n=An⊕Bn                              | (3) |

| P0=0                                    | (4) |

| $G_{m:n}=G_{n:k} + (P_{n:k} G_{k-1:n})$ | (5) |

| Pm:n=Pn:k· Pk-1:j                       | (6) |

| Sn=Pn⊕Cin                               | (7) |

|                                         |     |

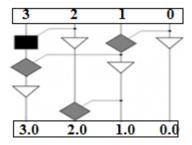

We might reduce power consumption and attain the high speed in the system with the use of Brent Kung adder prefix structure. BK adder is selected mostly for smallest fan-out and high speed in operation compared to other parallel prefix adder structure [9]. For instance, as in Figure 3 depicts the BK adder prefix structure with 3 main cells in the prefix structure.

Figure 3: 4-bit BK adder prefix structure

## 3. DESIGN METHODOLOGY

#### 4.

The procedure of designing a reverse converter is defined in this section. The selection of moduli set is the initial step involved in a reverse converter design. The moduli set selection is used to determine RNS's hardware realization,

dynamic range, and the speed. The 3 moduli set (2<sup>n</sup>-1, 2<sup>n</sup>,

$2^{n}+1$ ) were considered for the design, where n is a natural number. The importance of these moduli set is that they might be proficiently executed utilizing binary hardware, which leads to simple design and provides advantages of speed cost. The moduli values of the moduli set and the residue numbers must be substituted in CRT conversion procedure formulas. Here the residue number is the yield of the forward converter. The CRT conversion algorithm involves the calculation of recursive moduli inverse. The best way to implement moduli inverse is to save the constant in ROM, [10] which is then multiplied with the residue number

and then added using the adders. Arithmetic properties and propositions are used for simplifying the resulting equations. The final equations are realized by adder components like CPA-EAC, CSA-EAC, PPA, and CPA. The above said procedure is consolidated as the following algorithm. Step 1: Set the input

Step 2: Set the moduli set.

## 5. **RESULTS**

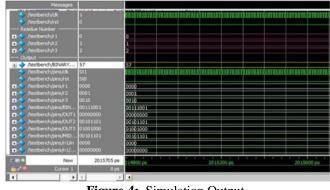

The circuit might be quantified and designed in Verilog. The

modulus set  $(2n-1, 2n, 2^{n}+1)$  was chosen. The Proposed system is simulated and verified using Model Sim ALTERA STARTER EDITION 6.4a. The below simulation result shows the output of the system as in figure 4 with n=2 for the above module set.

Figure 4: Simulation Output

The following Table represents the comparison of adders in terms of delay and frequency which is calculated using the tool Xlinix ISE 14.2 for the target device xc3s400e-5tq144.

| Table 1: Comparison of Adders in terms of Delay and |  |

|-----------------------------------------------------|--|

| Frequency                                           |  |

| ADDER | DELAY(ns) | FREQUENCY(MHz) |

|-------|-----------|----------------|

| RCA   | 12.804    | 78.102         |

| CLA   | 7.765     | 128.785        |

| CSA   | 7.626     | 131.129        |

| KS    | 2.257     | 443.095        |

| BK    | 2.021     | 494.841        |

Shown the above table 1 it has compare adders in terms of delay and frequency

## 6. CONCLUSION

In this paper the reverse converter was simulated. The above result shows that the reverse converter simulated using the BK parallel prefix adder network has less delay compared to other adders. The reverse converter was simulated for the  $\{2^{n}-1, 2n, 2n+1\}$  module set. This shows that the delay is reduced and the efficiency was improved.

P.Sowndarya Mala et al., International Journal of Advanced Trends in Computer Science and Engineering, 7(6), November -December 2018, 163-165

#### REFERENCES

A. Omondi and B. Premkumar, Residue Number Systems: Theory and Implementations. London, U.K.: Imperial College Press,2007.

https://doi.org/10.1142/p523

- [2] B. Parhami, Computer Arithmetic: Algorithms and Hardware Designs, 2nd ed., New York, NY, USA: Oxford Univ. Press, 2010.

- [3] J. Chen and J.Hu, -Energy-efficient digital signal processing via voltageoverscaling-based residue number system, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 21, no. 7, pp. 1322–1332, Jul. 2013.

- [4] C. H.Vun, A. B. Premkumar, and W. Zhang, -AnewRNS based DA approach for inner product computation, II IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 8, pp. 2139–2152, Aug. 2013.

- [5] S. AntãoandL. Sousa, -The CRNS frame work and its application to programmable and reconfigurable cryptography, ACM Trans. Archit. Code Optim., vol. 9, no. 4, p. 33, Jan. 2013.

- [6] A. S. Molahosseini, S. Sorouri, and A. A. E. Zarandi, -Research challengesin next-generation residue number system architectures, in Proc. IEEE Int. Conf. Comput. Sci. Educ., Jul. 2012, pp.1658–1661.

- [7] K.Navi, A. S. Molahosseini, and M. Esmaeildoust, -How to teach residue number system to computer scientists and engineers, IEEE Trans. Educ., vol. 54, no. 1, pp. 156–163, Feb. 2011.

https://doi.org/10.1109/TE.2010.2048329

- [8] Y.Wang, X. Song, M. Aboulhamid, and H.Shen, -Adder based residue to binary numbers converters for (2n − 1, 2n, 2n + 1), IEEE Trans. Signal Process., vol. 50, no. 7, pp. 1772–1779, Jul. 2002. https://doi.org/10.1109/TSP.2002.1011216

- [9] B.Cao,C. H.Chang, and T.Srikanthan, -An efficient everse converter forthe4- moduliset {2n-1, 2n, 2n+1,22n+1} based on the new Chinese remainder theorem, IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 50, no. 10, pp. 1296–1303, Oct. 2003.

- [10] A. S. Molahosseini, K.Navi, C. Dadkhah, O.Kavehei, and S. Timarchi, -Efficient reverse converter designs for the new 4-moduli sets {2n 1, 2n, 2n + 1, 22n+1 1} and {2n 1, 2n + 1, 22n, 22n + 1} based on new CRTs, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 823–835, Apr. 2010.

- [11] TrusilaMonyenyeNyandika, George Okeyo, Michael Kimwele," Enhancing Service Availability during Handover in Wireless Communication-Based Train Control Systems, International Journal of Advanced Trends in Computer Science and Engineering Volume 7, No.3, Pp-41-51, 2018.

- [12] Goodubaigari Amrulla, Murlidher Mourya, Rajasekhar Reddy Sanikommu,"A Survey of:Securing Cloud Data under Key Exposure", International Journal of Advanced Trends in Computer Science and Engineering, Volume 7, No.3, Pp-30-33, 2018.