Volume 7, No.6, November - December 2018

International Journal of Advanced Trends in Computer Science and Engineering

Available Online at http://www.warse.org/IJATCSE/static/pdf/file/ijatcse11762018.pdf

https://doi.org/10.30534/ijatcse/2018/11762018

Conventional Full Adder FinFET Implementation using Transmission Gate logic

<sup>1</sup>Ch.Rajesh Babu, <sup>2</sup>T Venkatesh, <sup>3</sup> E Jagadeeshwara Rao, <sup>4</sup>U V Raju

<sup>1,2,3,4</sup>, Department of ECE, Godavari Institute of Engineering & Technology, Rajahmundry, A.P, India.

## ABSTRACT

This paper examined the similar Investigation from claiming distinctive full adder phones with two rationale styles. Those rationale styles utilized for execution about FinFET based 1bit full snake need aid reciprocal MOS (CMOS) Furthermore transmission entryway (TG). The simulations from claiming full adders bring constantly completed during 10nm, 20nm Also 32nm innovation organization hub. This model may be dependent upon BSIM-CMG, a committed model for multigate units. Examination about execution Furthermore vitality proficiency of all sorts from claiming full adder cell outlines need been carried out. The execution measurements that were measured broke down Furthermore compared would Normal power, spillage power, delay and vitality. It is watched that little control is devoured previously, transmission entryway (TG) built full adder over those gathering full adder on 10nm innovation hub.

Keywords: Logic styles, Full adder, FinFET

# 1. INTRODUCTION

Presently day, the interest for packed in the secondary presents little energy Furthermore strong chip will be expanding step by step. That central processing unit (CPU) will be the center of every chip. That math logic unit (ALU) will be key component of chip spotted over CPU. ALU can perform intelligent procedure and fundamental math procedure, namely, addition, subtraction, multiplication, What's more division. The number-crunching operation could a chance to be performed as takes after: addition, negative addition, [1] [2] repeater addition, and repeater negative expansion. Done advanced framework to nanotechnology node, it may be required to plan a full snake similar to bring low control utilization, secondary velocity, vitality capable and dependable.

So, secondary velocity, low power, vitality capable, and dependable microprocessors are popular in the most recent Also imaginative silicon innovation organization methods have prompted those fast development for present day integrated chip (IC). The VLSI microprocessors could make tended to during Different plan levels for example, architectural, circuit, design and more creation. Outlining a math unit at An specific out level impacts its execution [3] Likewise Different execution figuring out elements for example, such that exchanging capacitance, move action Furthermore hamper present would determinedly impacted by decided rationale style. So, those target of the paper should figure out the best proficient rationale style the middle of CMOS Also TG to 1-bit full snake circlet.

# 2. OVERVIEW OF FINFET TECHNOLOGY

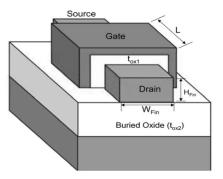

As shown the below figure 1 FinFET will be a non-planar gadget Hosting fin such as formed the place the entryway may be wrapped around Furthermore again the balance which goes about similarly as a transistor channel. It is additionally termed similarly as quasi-planar gadget concerning illustration those current streams parallel on wafer plane and the channel is peroxide blonde with wafer plane [4].

Figure 1: Block diagram of FinFET gate

Basically, FinFET may bring been organized with a chance to be constructed on silicon-on-insulator (SOI) wafers. Yet the scientists produced it sensibly with make normal for FinFETs will fill in for impostor silicon [5] wafers and move move forward the individuals execution depended with respect to certain parameters..

Capable channel length Leff = Lgate +  $2 \times \text{Lext}$  (1) capable channel width w = Tfin +  $2 \times \text{Hfin}$  (2). Those put Hfin Furthermore Tfin those balance tallness and additionally thickness respectively, Lgate might make length of the gate, Lext is extended sourball or channel area Concerning outline showed in fig. 1. Balance width (Tfin) expects a critical a major aspect to directing the individuals short channel sway viably. Subsequently Tfin ~ Lgate/2 might make emulated. Similarly as a FinFET structure, a ultra-thin si balance sorts a administering channel wherein [6] the individuals electrons stream from hotspot for channel. This Steering channel might a chance to be wrapped toward entryway the place enter voltages compelling reason with make supplied. Subsequently regulating the stream of electrons much in off state keeping those spillage for present. Now and then there is the measure about accuse transporters and the rate during which it flows, bringing about the breakdown of the leading channel framed toward single balance. This obstructs the stream for electrons starting with wellspring should channel which ceases those current stream[7-9] Those number from claiming balances is expanded for multi-gate field-effect transistors (MuGFET) which need aid constructed parallel on one another( enhancing short channel impact. Similarly as the number from claiming balances increases, the measure from claiming accuse transporters streaming from higher possibility with bring down possibility additionally increments. Therefore, the rate during which those transporters stream will be quicker expanding the exchanging velocity. The fundamental playing point for various balances will be better entryway control again those leading channel. Because of this, there will be a leakage reduction in current. This attains high current on this stage. FinFETs[8] bring different logic designing styles about distinctive FinFETs; one circuit make arranged to a standout among the ensuing modes such as shorted gate mode, independent gate mode, low power mode, mixture LG/LP mode.

## 3. LOGIC STYLE

**3.1** Rationale style of a circuit effects its speed, compel indulgence, measure What's more likewise cabling flightiness. Those crazy delay depends upon the measure from claiming transistors over series, transistor sizes Furthermore wiring capacitance. Generosity with reverence with voltage and transistor scaling Also Moreover variety process, endeavoring states Also comparability to including circuits would noteworthy viewpoints impacted by executing rationale style.

## 3.2 Logic style of Complementary MOS(CMOS)

Logic style of Complementary MOS combines for more than one networks, the PUN & PDN and it comprise a link in between PMOS and pull down method comprise of NMOS device. Those capacities from claiming pull up system is with provide association between the gate o/p and  $V_{dd}$ , anytime that o/p of the gate is intended to be high. Similarly, work for pull down system may be with provide association between the gate o/p and GND anytime those o/p of the gate will be intended to be low..

## 3.3 Transmission Gate (TG):

It comprises over n-channel transistor Also Additionally pchannel transistor with differentiate entryway acquaintance ships Also an normal wellspring also channel co operations. That control indicator will be associated with entryway to nchannel transistor and likewise its supplement will be associated of the entryway to p-channel transistor.

## Full Adder Functional Simulation

Summation will be the vast majority fundamental operation and used in advanced device and arithmetic logic unit (ALU) will include many numbers. The regularly utilized adder cell is full adder where we place three inputs i. E. A, b and also  $C_{IN}$  will be included together for calculation of  $C_{OUT}$ . The  $C_{OUT}$  is given by:

#### **Table 1:** Truth table of full adder (1 bit)

| INPUTS |   | OUTPUTS |     |       |

|--------|---|---------|-----|-------|

| Α      | в | С       | sum | carry |

| 0      | 0 | 0       | 0   | 0     |

| 0      | 0 | 1       | 0   | 1     |

| 0      | 1 | 0       | 0   | 1     |

| 0      | 1 | 1       | 1   | 0     |

| 1      | 0 | 0       | 0   | 1     |

| 1      | 0 | 1       | 1   | 0     |

| 1      | 1 | 0       | 1   | 0     |

| 1      | 1 | 1       | 1   | 1     |

Those CMOS full adder need 28 transistors in the o/p and it may be the simplest usage In light of over equations. That circuit CMOS 1-bit full adder has shown the table 1. The advantages incorporate high noise margin dependable on low voltage [10] However, high amount of transistors might bring vast power consumption, high i/p loads and requires bigger silicon zone in a wafer. It likewise stated that this design might introduce more delay due to the reason that i/p created from  $C_{out}$  as i/p might be watched from figure 2.

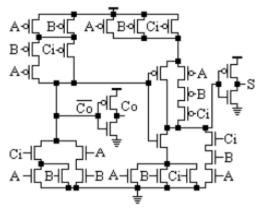

### 3.4 I bit transmission gate full adder

Transmission gates of full adder comprises about 20 transistors which aggravated up about transmission gates, PMOS and NMOS transistors Likewise illustrated for fig. 3. Transmission gate are utilized within the configuration in light it need secondary speed operation and low force dispersal. Those TG full adder output may be simpler over CMOS with adjusted era for aggregate Also  $C_{out}$  yield signals also less than transistor count compared to the lower i/p load. Contrasted for CMOS full adder, TG full snake need higher energy dispersal. It will be likewise said that accepting that TG full snake will be cascaded completed series [11] the individuals proliferation delay additionally could expand exorbitantly as shown in figure 3.

Figure 2: Bit CMOS Full Adder [3]

Figure 3: Bit TG Full Adder [3]

Table 2: Parameters utilized within experimentation of full adder

| Parameters                       | Value    |          |

|----------------------------------|----------|----------|

| Technology node                  | 20nm     | 10nm     |

| Supply Voltage(Vdd)              | .7v      | .7v      |

| Capacitance                      | 14.5332f | 14.5332f |

| Fin Width(T <sub>FIN)</sub>      | 15n      | 9n       |

| Fin Length(Lg)                   | 24n      | 14n      |

| Fin Height(H <sub>FIN)</sub>     | 28n      | 21n      |

| Number of Fin(N <sub>FIN</sub> ) | 1        | 1        |

TG built engineering organization hub. Every of the Mobile plans is executed to figure out the ideal tradeoff the middle of delay-energy-power On 10nm, 20nm and 32nm over advanced system parameters shown I table 2.

## 4. RESULTS & ANALYSIS

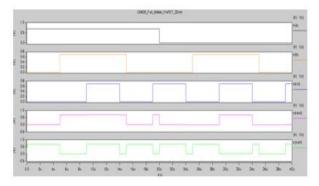

The execution measurements of the full adder calculated would control, delay Also vitality. Those Recreation Investigation will be finished In HSPICE and waveforms are watched ahead Cosmos Scope. The Recreation Investigation will be conveyed crazy with inputs A,B,C and outputs sum and about this full adder circuit. That reproduction waveform of power, delay and vitality from claiming FinFET based circuits' parameters shown in table 3.

| Parameter     | CMOS                    | TG       |

|---------------|-------------------------|----------|

| Average       | 3.2759x 10 <sup>-</sup> | 3.8245 x |

| Delay(sec)    | 4.0000 x                | 3.2000 x |

| Energy(joule) | 6.5525 x                | 5.8212 x |

| Leakage       | 6.5525 x                | 5.8212 x |

| Leakage       | 9.3608 x                | 8.3160 x |

| EDP(joule)    | 2.6535 x                | 3.4420 x |

| PDP(joule)    | 2.9483 x                | 3.9780 x |

# 4.1 CMOS and TG Logic styles with 1 bit full adder at 10 nm tool parameter

Tallness of the balance (HFIN) will be 21nm, thickness of the balance may be 9nm furthermore somewhere else length (lg) is 14n. Table6 demonstrates execution parameter from claiming FinFET built in table 5.

| Table 5: shows | the parameter | performance |

|----------------|---------------|-------------|

|----------------|---------------|-------------|

| Parameter            | CMOS                       | TG                         |

|----------------------|----------------------------|----------------------------|

| Average Power(watts) | 1.1085 x 10 <sup>-9</sup>  | 1.5395 x 10 <sup>-9</sup>  |

| Delay(sec)           | 1.4972x10 <sup>-8</sup>    | 1.4983x10 <sup>-8</sup>    |

| Energy(joule)        | 7.2275 x 10 <sup>-15</sup> | 1.2772 x 10 <sup>-14</sup> |

| Leakage Power(watts) | 7.2275 x 10 <sup>-7</sup>  | 1.2772 x 10 <sup>-6</sup>  |

| Leakage Current(amp) | 1.0325 x10 <sup>-0</sup>   | 1.8246 x10 <sup>-0</sup>   |

| EDP(joule)           | 2.4580x 10 <sup>-19</sup>  | 2.3067 x 10 <sup>-14</sup> |

| PDP(joule)           | 1.6597x 10 <sup>-14</sup>  | 3.4561 x 10 <sup>-19</sup> |

## 4.2 Comparison study of presentation mode

Here execution of normal energy indulgence, delay, spillage control, force delay item and more vitality delay result metric will be investigated. This metric will be measured to CMOS.

#### 5. CONCLUSION

This paper investigated those Mobile configuration may be additionally central point which contributes on useful execution of advanced circuits. So, it might have been checked that those 1-bit transmission entryway (TG) FinFET built full adder delicately a diminished sum about PDP Also EDP contrasted with different cell configuration due to its high-sounding execution Furthermore full swing operation in 10nm innovation hub. In view of those findings, the 1-bit FinFET-based full snake toward 10nm innovation hub might have been indicated will make those least Also ideal tradeoff on the whole metric exhibitions. It is recommended that come fill in about this research ought to incorporate the finish math rationale unit (ALU) configuration. Furthermore that, the execution and possibility from claiming different rationale style for example, Stagnant Energy- recuperation full adder and mixture CMOS full snake ought to be investigated over outlook fill in.

## REFERENCES

- A.Chandrakasan, W.Bowhill, and, F. Fox, Design of High Performance Microprocessor Circuitsl, IEEE Journal of Solid-State Circuits, Vol.36, No.10, pp. 263 -271, Aug. 2001.

- [2] Weiqiang Zhang, Linfeng Li, and Jianping Hu, Design Techniques of P-Type CMOS Circuits for Gate-Leakage Reduction in Deep Sub-micron ICsl IEEE 2009

- [3] A. M. Shams, T. K. Darwish, and M.A. Bayoumi, Performance analysis of low-power 1-bit CMOS full adder cells, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 10, no. 1, pp. 20–29, 2002.

- [4] ITRS, International Technology Roadmap for Semiconductor (ITRS) updated, 2006,

- [5] T. J. K. Liu, FinFET history, fundamentals and future, in Proceedings of the Symposium on VLSI Technology Short Course, University of California, Berkeley, Calif, USA, June 2012

- [6] Vojin G. Oklobdzija, Differential and Pass Transistor CMOS Logic for High Performance Systems, Proc. 21st International Conference on Microelectronics, Vol. 2, Sep 1997, pp. 679-688.

- [7] V. S. Basker, T. Standaert, H. Kawasaki, C.-C.Yeh, K. Maitra, —A 0.063 μm2 FinFET SRAM cell demonstration

.

with conventional lithography using a novel integration scheme with aggressively scaled fin and gate pitch IEEE Symposium on VLSI Technology Digest of Technical Papers, pp.19-20,2010

- [8] Vita Pi-Ho Hu, Ming-Long Fan, Chien-Yu Hsieh, PinSu, and Ching-Te Chuang, —FinFET SRAM Cell Optimization Considering Temporal Variability Due to NBTI/PBTI, Surface Orientation and Various Gate Dielectricsl, IEEE Transactions on Electron Devices, Vol. 58, No. 3, pp.805-811, March 2011

- [9] Wayne Wolf —Case study of Reliability-aware and Low power design in IEEE transactions on very large scale integration (VLSI) systems, vol. 16, no. 7, July 2008

- [10] Wen-TsongShiiie, —Leakage Power Estimation and Minimization in VLSI Circuits I, IEEE 2001

- [11] Xin Zhao, —A Novel Low-Power Physical Design Methodology for MTC MOSI in IEEE conference, Vol.12, No.9, pp. 185-190, Nov 2012